Я проектирую MIPS-подобный процессор с Verilog, и теперь я работаю с опасностями данных.У меня есть следующие инструкции:

Ins[0] = LW r1 r0(100)

Ins[1] = LW r2 r0(101)

Ins[2] = ADD r3 r2 r1

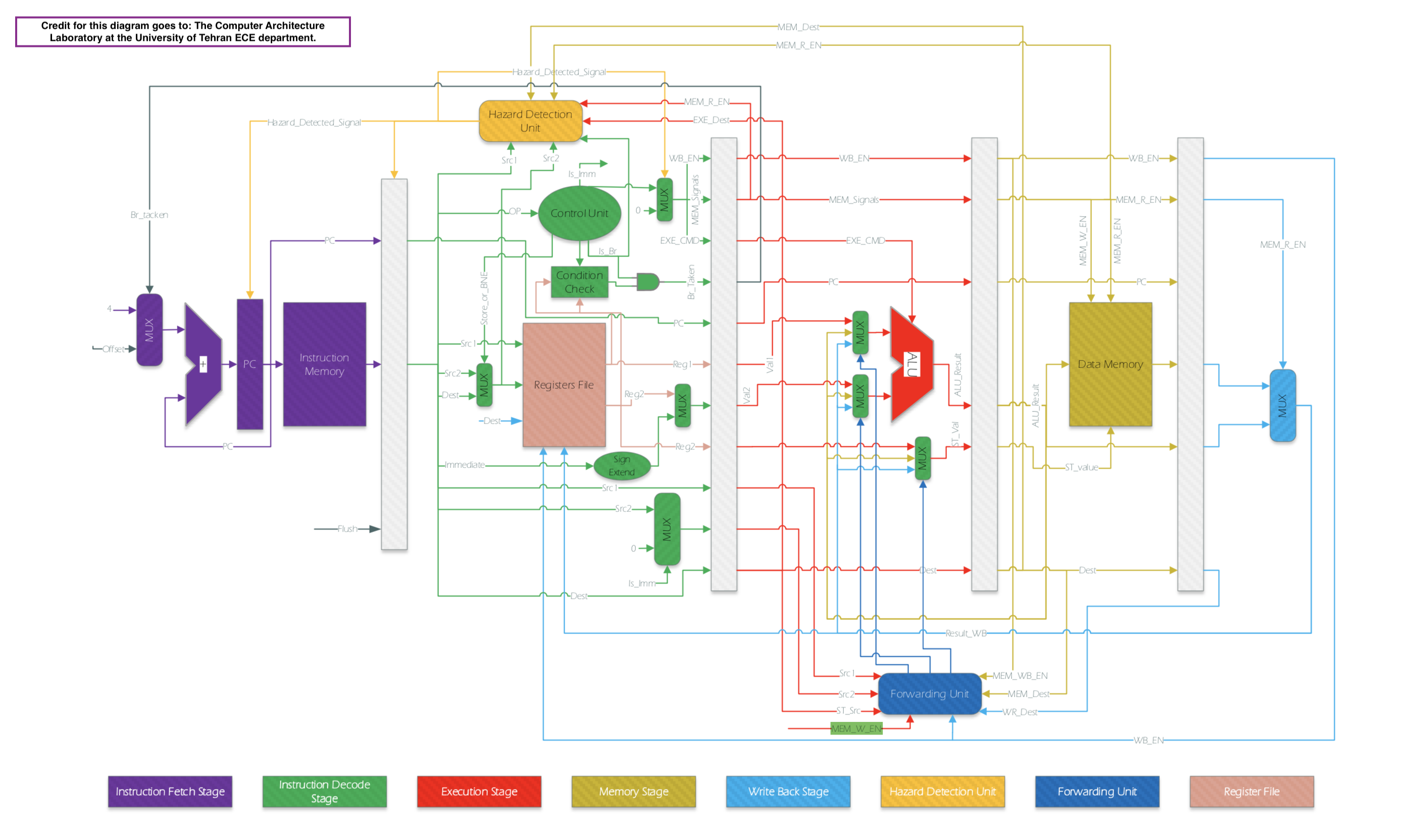

Я использую конвейер, и мой dataPath выглядит примерно так:  У меня 5 ступеней, с 4 буферами-защелками, разделяющими их.

У меня 5 ступеней, с 4 буферами-защелками, разделяющими их.

Проблема в том, что когда инструкция ADD достигает стадии 3 (где ALU должен вычислять r1 + r2), инструкция 1 (второй LW) находится на стадии 4 и еще не прочитала адрес памяти r0 + 101,поэтому я должен остановить один цикл, и после этого Ins1 достигнет последней стадии.

В этой ситуации первый LW завершил свою работу, и новое значение r1 отсутствует в dataPath, но мне нужно передать этозначение для входа B ALU.

(Это называется пересылкой данных, потому что когда третья инструкция находилась на этапе 2, значение r1 не было готово, и я должен переслать его с более поздних этапов (синие провода, которые приходятиз последнего MUX и перейдите к ALU MUX), но из-за остановки второго LW у меня нет значения r1.

Спасибо за любую помощь.